给初学者的

一直有很多人问我阻抗怎么计算的. 人家问多了,我想给大家整理个材料,于己于人都是个方便.如果大家还有什么问题或者文档有什么错误,欢迎讨论与指教!

在计算阻抗之前,我想很有必要理解这儿阻抗的意义。

传输线阻抗的由来以及意义

传输线阻抗是从电报方程推导出来(具体可以查询微波理论)

如下图,其为平行双导线的分布参数等效电路:

从此图可以推导出电报方程

取传输线上的电压电流的正弦形式

得

推出通解

定义出特性阻抗

无耗线下r=0, g=0 得

注意,此特性阻抗和波阻抗的概念上的差异(具体查看平面波的波阻抗定义)

特性阻抗与波阻抗之间关系可从

Ok,

理解特性阻抗理论上是怎么回事情,看看实际上的意义,当电压电流在传输线传播的时候,如果特性阻抗不一致所求出的电报方程的解不一致,就造成所谓的反射现

象等等.在信号完整性领域里,比如反射,串扰,电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来.

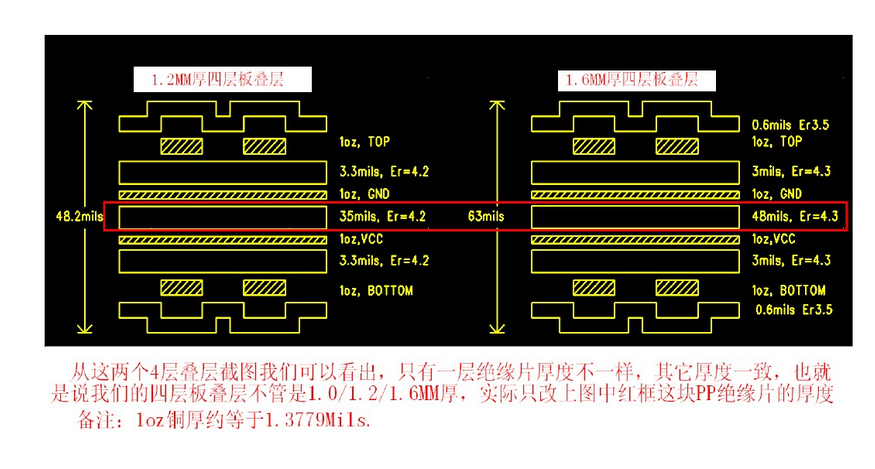

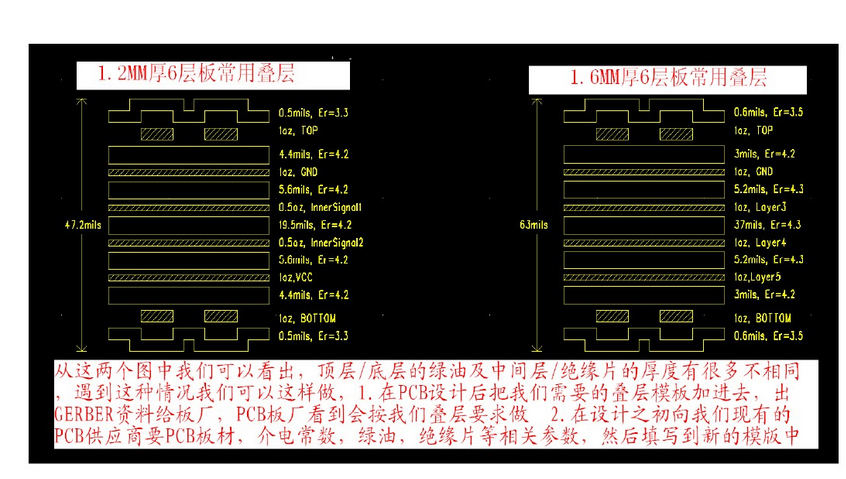

叠层(stackup)的定义

我们来看如下一种stackup,主板常用的8 层板(4 层power/ground 以及4 层走线层,sggssggs,分别定义为L1, L2…L8)因此要计算的阻抗为L1,L4,L5,L8

下面熟悉下在叠层里面的一些基本概念,和厂家打交道经常会使用的

Oz 的概念

Oz 本来是重量的单位Oz(盎司 )=28.3 g(克)

在叠层里面是这么定义的,在一平方英尺的面积上铺一盎司的铜的厚度为1Oz,对应的单位如下

介电常数(DK)的概念

电容器极板间有电介质存在时的电容量Cx 与同样形状和尺寸的真空电容量Co之比为介电常数:

ε = Cx/Co = ε’-ε”

Prepreg/Core 的概念

pp 是种介质材料,由玻璃纤维和环氧树脂组成,core 其实也是pp 类型介质,只不过他两面都覆有铜箔,而pp 没有.

传输线特性阻抗的计算

首先,我们来看下传输线的基本类型,在计算阻抗的时候通常有如下类型: 微带线和带状线,对于他们的区分,最简单的理解是,微带线只有1 个参考地,而带状线有2个参考地,如下图所示

对照上面常用的8 层主板,只有top 和bottom 走线层才是微带线类型,其他的走线层都是带状线类型

在计算传输线特性阻抗的时候, 主板阻抗要求基本上是:单线阻抗要求55 或者60Ohm,差分线阻抗要求是70~110Ohm,厚度要求一般是1~2mm,根据板厚要求来分层得到各厚度高度.

在此假设板厚为1.6mm,也就是63mil 左右, 单端阻抗要求60Ohm,差分阻抗要求100Ohm,我们假设以如下的叠层来走线

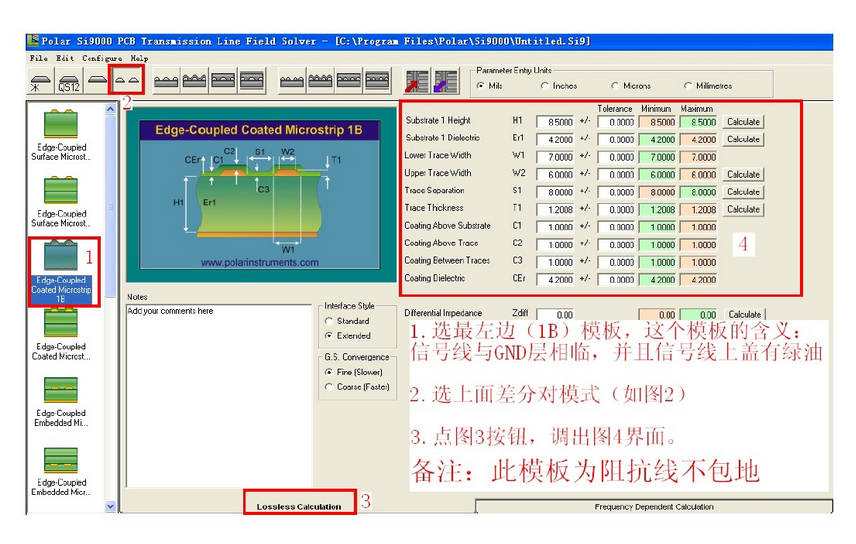

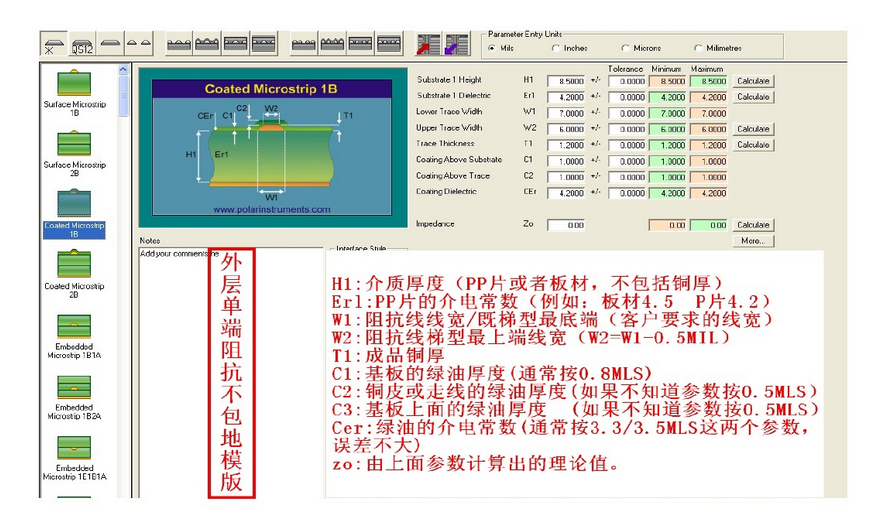

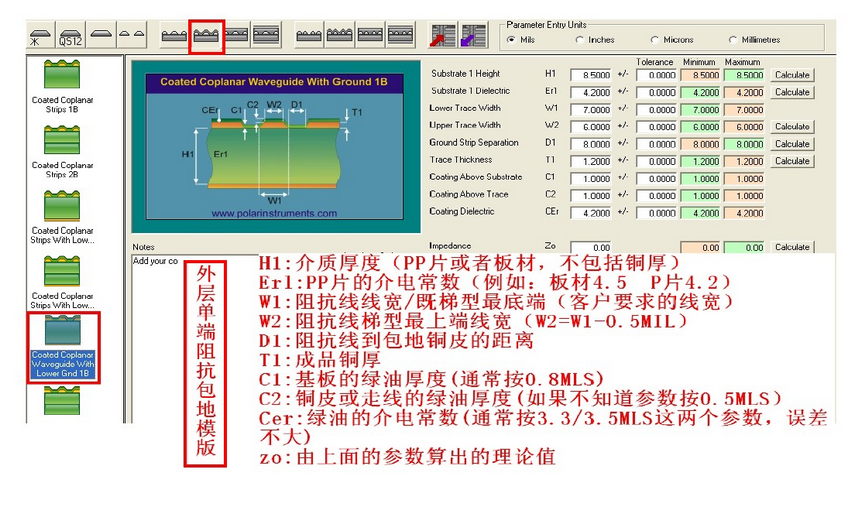

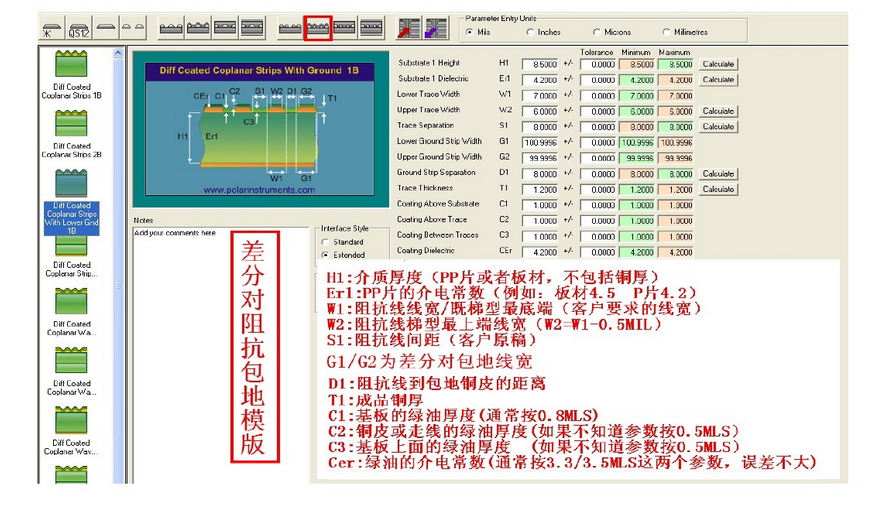

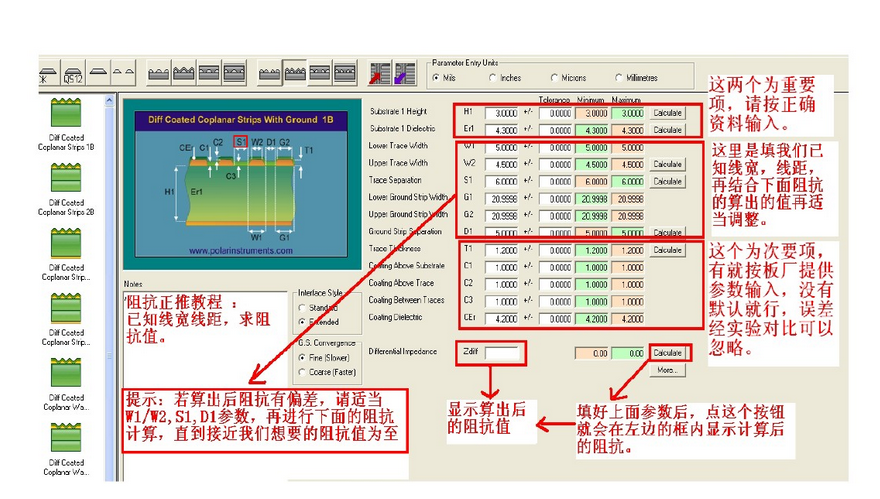

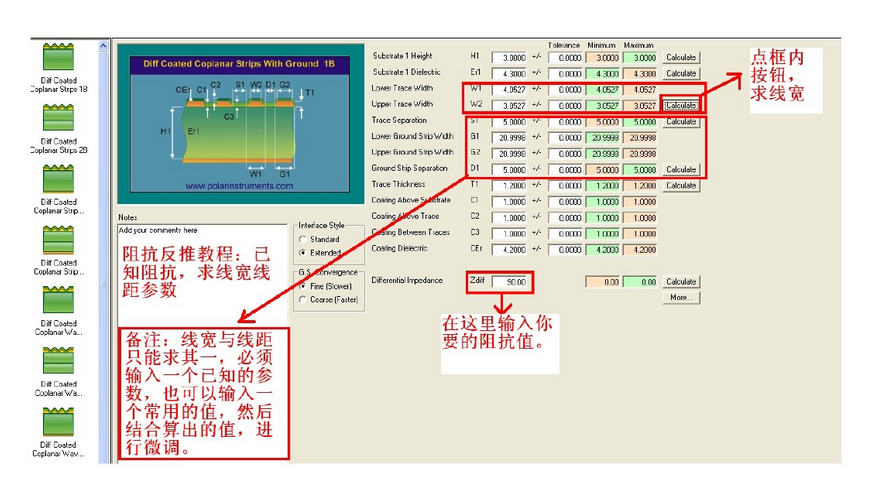

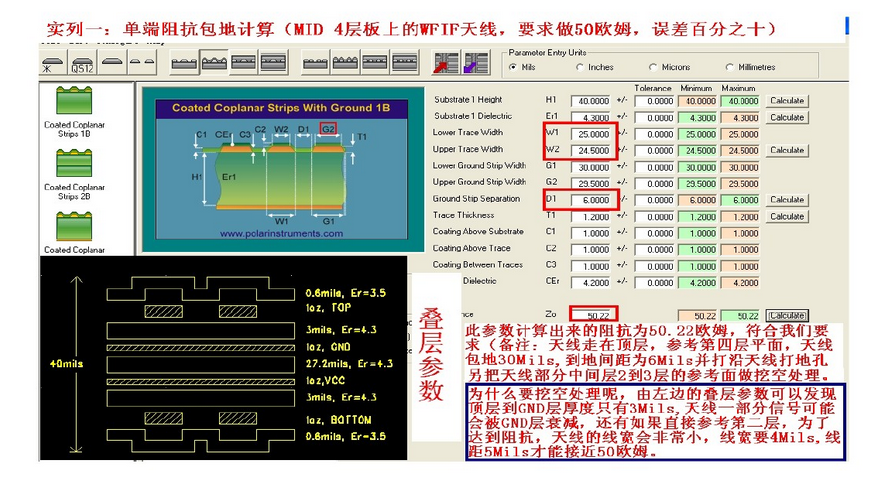

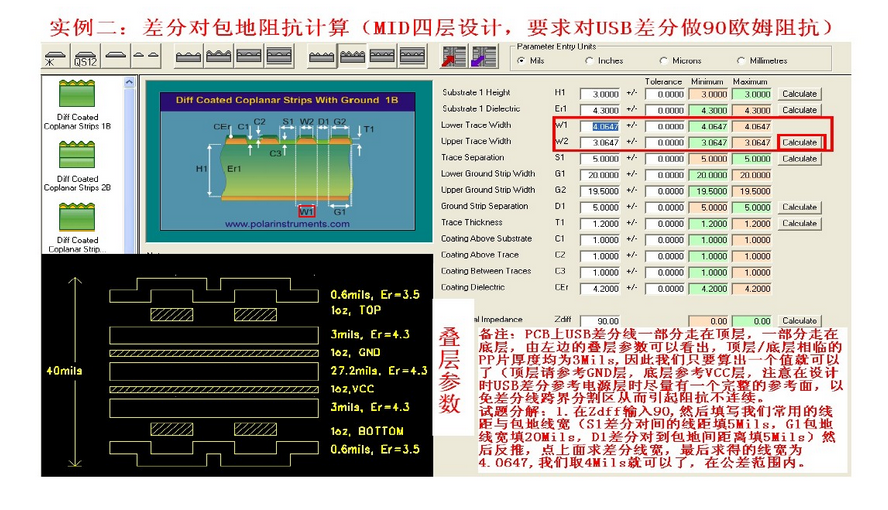

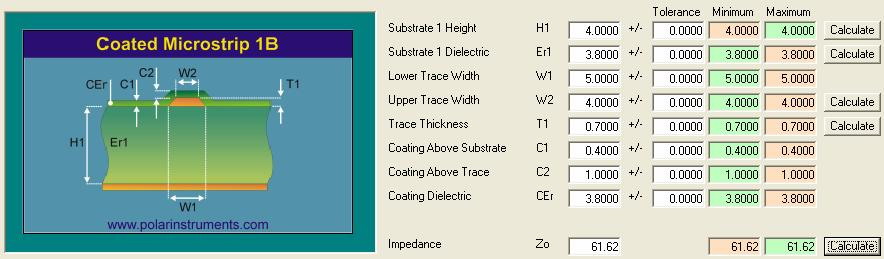

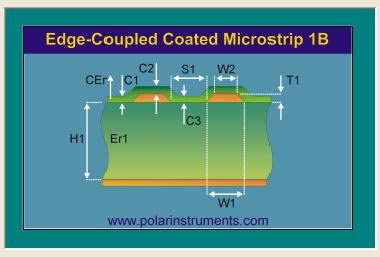

先来计算微带线的特性阻抗,由于top 层和bottom 层对称,只需要计算top 层阻抗就好的,采用polar si6000,对应的计算图形如下:

在计算的时候注意的是:

1,你所需要的是通过走线阻抗要求来计算出线宽W(目标)

2,各厂家的制程能力不一致,因此计算方法不一样,需要和厂家进行确认

3,表层采用coated microstrip 计算的原因是,厂家会有覆绿漆,因而没用surface microstrip 计算,但是也有厂家采用surface microstrip 来计算的,它是经过校准的

4,w1 和w2 不一样的原因在于pcb 板制造过程中是从上到下而腐蚀,因此腐蚀出来有梯形的感觉(当然不完全是)

5,在此没计算出精确的60Ohm 阻抗,原因是实际制程的时候厂家会稍微改变参数,没必要那么精确,在1,2ohm 范围之内我是觉得没问题

6,h/t 参数对应你可以参照叠层来看

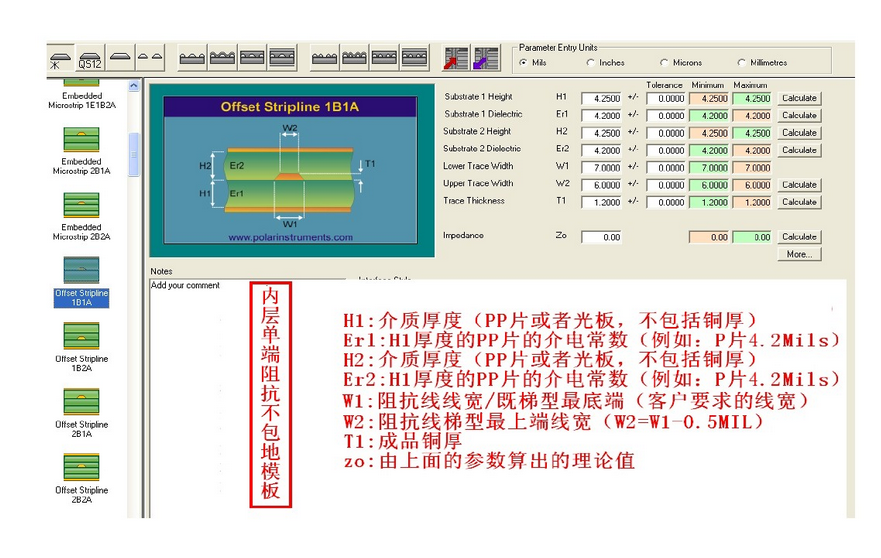

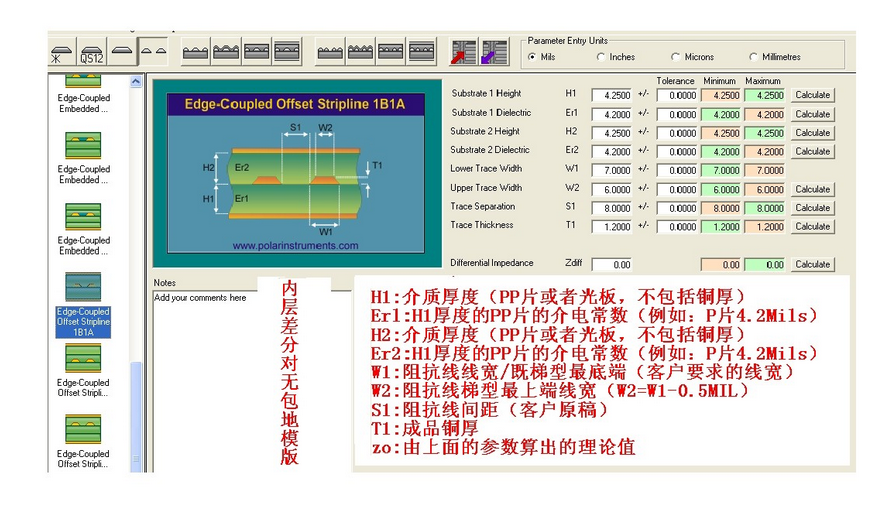

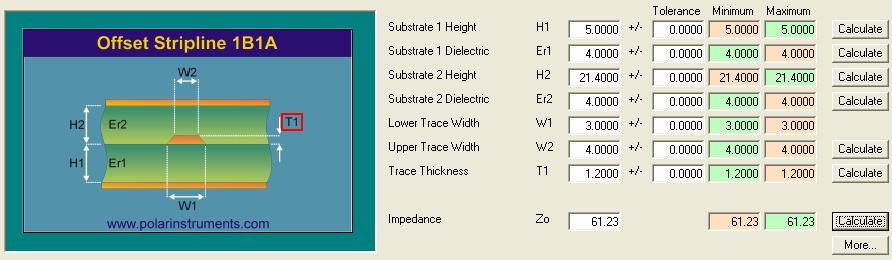

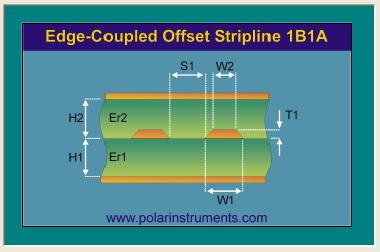

再计算出L5 的特性阻抗如下图

记得当初有各版本对于stripline 还有symmetrical stripline 的计算图,实际上的差异从字面来理解就是symmetrical stripline 其实是offset stripline 的特例H1=H2

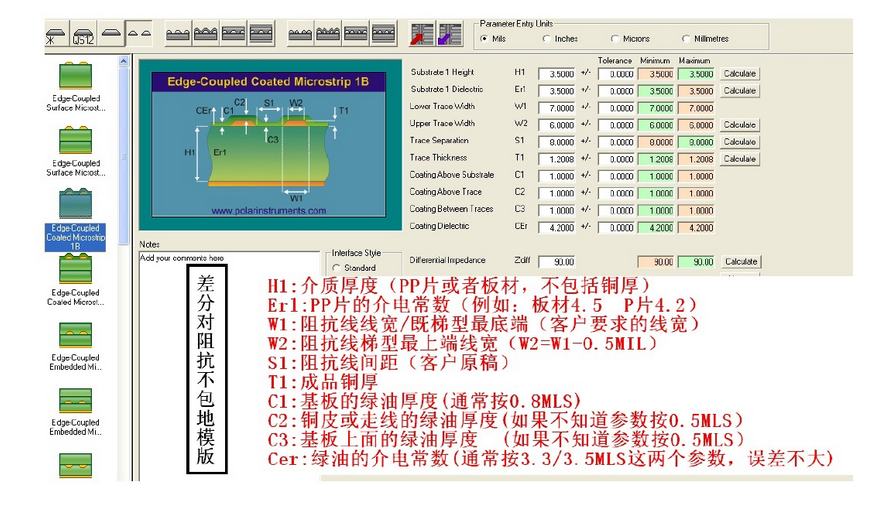

在计算差分阻抗的时候和上面计算类似,除所需要的通过走线阻抗要求来计算出线宽的目标除线宽还有线距,在此不列出

选用的图是

在计算差分阻抗注意的是:

1,

在满足DDR2 clock 85Ohm~1394 110Ohm

差分阻抗的同时又满足其单端阻抗,因此我通常选择的是先满足差分阻抗(很多是电流模式取电压的)再考虑单端阻抗(通常板厂是不考虑的,实际做很多板子,问

题确实不算大,看样子差分线还是走线同层同via 同间距要求一定要符合)

———-谨以此文怀念初学SI 的艰苦岁月。

特性阻抗公式 (含微带线,带状线的计算公式)

a.微带线(microstrip)

Z={87/[sqrt(Er+1.41)]}ln[5.98H/(0.8W+T)]

其中,W为线宽,T为走线的铜皮厚度,H为走线到参考平面的距离,Er是PCB板材质的介电常数(dielectric

constant)。此公式必须在0.1<(W/H)<2.0及1<(Er)<15的情况才能应用。

b.带状线(stripline)

Z=[60/sqrt(Er)]ln{4H/[0.67π(0.8W+T)]} 其中,H为两参考平面的距离,并且走线位于两参考平面的中间。此公式必须在W/H<0.35及T/H<0.25的情况才能应用

差分阻抗的计算方法及公式

The Differential Impedance Calculator is provided free to registered users. Please Register here

Instructions:

1. Select the number of substrate layers required.

2. You will then be presented with a table representing the suggested stack-up for that type of substrate.

3. Modify the variables to examine the effects on the trace Characteristic and Differential Impedance.

Important: The trace separation should not be adjusted to alter the Differential

Impedance – trace separation should always be kept to the minimum

clearance specified by the PCB vendor.

Note:

1. All dimensions are in MIL (thousands of an inch).

2. The Dielectric Constant of FR4 material may vary by as much as 20% (4.2 to 5.2).

3. The overall Dielectric Thickness (Cu to Cu) should total 62 MIL nominally.

4. Variables unavailable for modification have no significant effect on the impedance of the traces.

5. The default multilayer board stack-ups are taken from Advance Design for SMT, Barry Olney/AMC.

6. The Impedance Calculator uses formulae derived from:

? IPC-D-317 – Design Standard for Electronic Packaging Utilizing High Speed Techniques.

? EMC & the Printed Circuit Board – Montrose.

7. Only Edge

Coupled Differential Pairs are considered. No allowance has been made

for Broad Side Coupling from adjacent layers. It is good practice to

route adjacent layers orthogonal to each other in order to reduce any

coupling that may occur.

8. To reduce EMI, high frequency, fast rise time signals should be routed between the reference planes.

All care has been taken to ensure that the results are correct but no responsibility is taken for any errors.

If you prefer to do the calculations yourself – please use the formulae below.

|

Microstrip Differential Impedance (for traces routed on an outer layer) |

Unbalanced Stripline Differential Impedance (for traces embedded between planes) |

|---|---|

|

Zo = [87/Sqrt(Er+1.41)]* ln(5.98H/(0.8W+T)) Zdiff = 2*Zo (1 ? 0.48 e-0.96D/H) |

Zo = [80/Sqrt Er]* ln(1.9(2H+T)/(0.8W+T)) * (1 – (H / 4(H + C + T))) Zdiff = 2*Zo (1 ? 0.347 e-2.9D/B) |

where

W = trace width

T = trace thickness

H = distance to nearest reference plane

Er = dielectric constant

D = trace edge to edge spacing

C = signal layer separation

B = reference plane separation

| Material | Dielectric Constant |

|---|---|

| FR4 Fiberglass Epoxy | 4.7 |

| Teflon | 2.2 |

| Teflon Glass | 2.5 |

| Polyimide | 3.5 |

| Polyimide Glass | 4.2 |

Relative Dielectric Constants of substrate materials

PCB阻抗设计详解

1、前言

随着科技发展, 尤其在积体电路的材料之进步,使运算速度有显著提升, 促使积体电路走向高密度?小体积, 单一零件,

这些都导致今日及未?的印刷电路板走向高频响应, 高速率数位电路之运用,

也就是必?控制线路的阻抗?低失真?低干扰及低串音及消除电磁干扰EMI。阻抗设计在PCB设计中显得越来越重要。作为PCB制造前端的制前部,负责阻抗

的模拟计算,阻抗条的设计。客户对阻抗控制要求越来越严,而阻抗管控数目也原来越多,如何快速,准确地进行阻抗设计,是制前人员非常关注的一个问题。

2、阻抗主要类型及影响因素

阻抗(Zo)定义:对流经其中已知频率之交流电流所产生的总阻力称为阻抗(Zo)。对印刷电路板而言,是指在高频讯号之下,某一线路层(signal layer)对其最接近的相关层(reference plane)总合之阻抗。

2.1 阻抗类型:

(1)特性阻抗 在计算机?无线通信等电子信息产品中, PCB的线路中的传输的能量, 是一种由电压与时间所构成的方形波信号(square wave signal, 称为脉冲pulse),它所遭遇的阻力则称为特性阻抗。

(2)差动阻抗 驱动端输入极性相反的两个同样信号波形,分?由两根差动线传送,在接收端这两个差动信号相?。差动阻抗就是两线之?的阻抗Zdiff。

(3)奇模阻抗 两线中一线?地的阻抗Zoo,两线阻抗值是一致。

(4)偶模阻抗 驱动端输入极性相同的两个同样信号波形, ?两线连在一起时的阻抗Zcom。

(5)共模阻抗 两线中一线对地的阻抗Zoe,两线阻抗值是一致,通常比奇模阻抗大。

其中特性和差动为常见阻抗,共模与奇模等很少见。

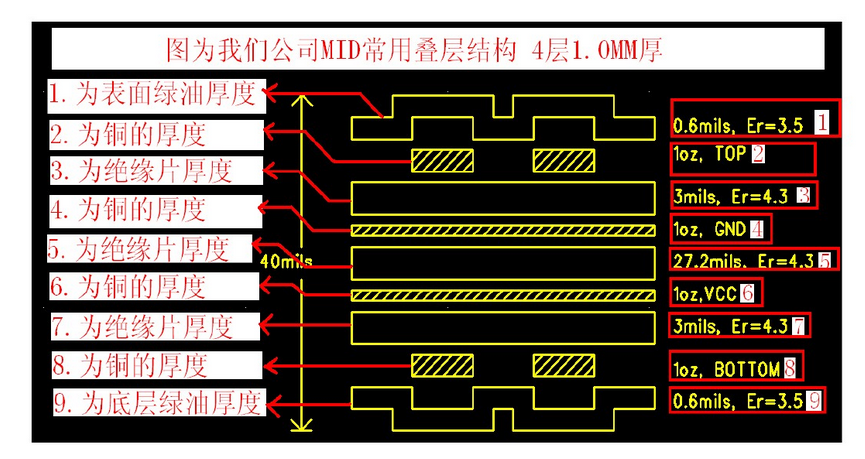

2.2 影响阻抗的因素:

W—–线宽/线间 线?增加阻抗变小,距离增大阻抗增大;

H—-绝缘厚度 厚度增加阻抗增大;

T——铜厚 铜厚增加阻抗变小;

H1—绿油厚 厚度增加阻抗变小;

Er—–介电常数 参考层 DK值增大, 阻抗?小;

Undercut—-W1-W undercut增加, 阻抗?大。

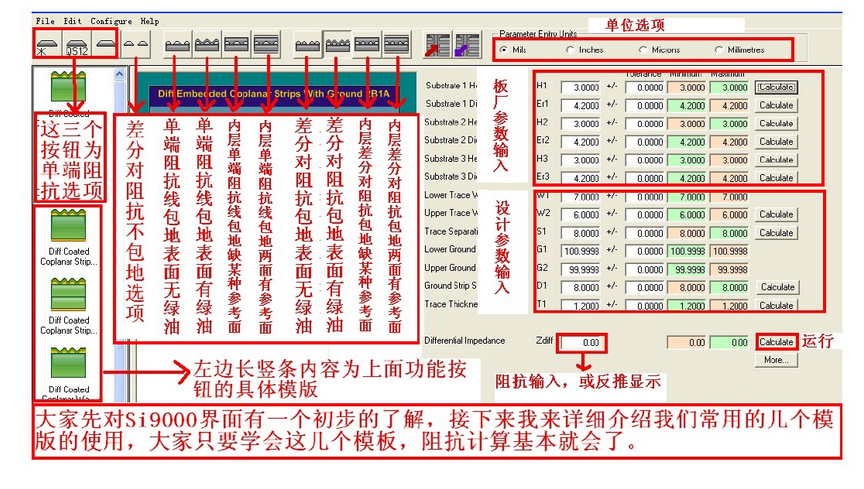

3、阻抗计算自动化

如今,我们业界最常用的阻抗计算工具是Polar公司提供的Si8000 Field

Solver,Si8000是全新的边界元素法场效解计算器软件,建立在我们熟悉的早期Polar阻抗设计系统易于使用的用户界面之上。此软件包含各种阻

抗模块,人员通过选择特定模块,输入线宽,线距,介层厚度,铜厚,Er值等相关数据,可以算出阻抗结果。一个PCB阻抗管控数目少则4,5组,多则几十

组,每一组的管控线宽,介层厚度,铜厚等都不同,如果一个个去查数据,然后手动输入相关参数计算,非常费时且容易出错。

下面,将介绍如何通过业界领先的制前设计工程软件解决方案供货商奥宝科技的InPlan软件,自动地进行阻抗设计,大幅提高制前工作效率。

奥宝科技的InPlan系统,可与Si8000连接,在以下数据库建立的基础上,自动计算阻抗:首先,在InPlan建立完整的物料库,按不同厂商,型号归类。建入依厂内实际制程参数得出的压合厚度,基板铜厚,PP含胶量等数据。

然后,在InPlan里建立算阻抗的规则Rule,如绿油厚度,Undercut值也可根据不同的铜厚,阻抗模块或内外层的不同设定规则。介电

常数则主要根据材料种类,阻抗模块的不同分别写入公式。阻抗值,阻抗线宽公差也通过InPlan

Rule写入规则。算阻抗时,InPlan根据规则自动带出相关的阻抗影响参数值,算出最优化的阻抗结果。且不管有多少组阻抗,只需点一个按钮,几秒钟的

时间就可以得出所有结果。

4、自动生成阻抗条

如果客??有自己设计阻抗条,

我们就需要自行设计阻抗条放于板边或者折断边上(一般情?下阻抗条放于折断边需要客?的同意)。电路板制造商在电路板边设计满足客?阻抗控制所有特征及参

数的阻抗条,通过测试阻抗条的阻抗值,反映出电路板达到客?阻抗控制要求。要正确测试板内阻抗值,关键在于阻抗条的设计。

一般PCB厂阻抗条设计方式为:MI工程师根据算出的阻抗结果填写阻抗附件表格,如阻抗值,参考层,管控线宽,测试孔,参考层属性(正负片)等。

然后,CAM工程师根据MI提供的阻抗表格,手动制作阻抗条,或通过Script,输入相关阻抗数据,用程式跑阻抗条。一般情?下, 一种阻抗值我们就设计一个阻抗条,制作一个阻抗条,一般都需10来分钟,重复的手动数据填写,非常费时,且容易出错。

我们可通过奥宝的InCoupon

功能,将阻抗条的相关规则建入系统,可自动产生高品质阻抗条,直接导入Genesis系统。InCoupon

采用嵌入式发展架构,在半成品层级时即能侦测出层板间最理想的钻孔位置,使现有板层的钻孔作业可与 Coupon 线路层之间完全吻合,整合了完整的

CAM 与工程技术,产生出阻抗量测用的Coupon线路、发展架构与半成品表,并且可对Coupon

层级找出最理想的相互连接能力,以智慧型操作精灵取代复杂、手动计算,可在数秒间自动运算出可靠的量测线路Coupon,让Coupon

的设计变成一项简单且标准的工作。

5、总结

PCB的竞争越来越激烈,样品交期越来越短,阻抗设计在制前工作中占了很大的比例,如何缩短阻抗制作时间,做出满足客户要求的阻抗匹配,是制前

部必需考虑的一个问题。InPlan和InCoupon的出现,给阻抗设计提供了很好的帮助。当然,各PCB板厂自己的阻抗计算规则,Layout方式与

大小都会不一样,InPlan系统需专人进行开发,维护,才能真正实现其功能。但相信,阻抗设计的自动化,将在PCB制前部越来越普及。